[ad_1]

As I’m positive lots of you recognize, x86 structure has been round for fairly a while. It has its roots in Intel’s early 8086 processor, the primary within the household. Certainly, even the unique 8086 inherits a small quantity of architectural construction from Intel’s 8-bit predecessors, courting all the best way again to the 8008. However the 8086 advanced into the 186, 286, 386, 486, after which they received names: Pentium would have been the 586.

Alongside the best way, new directions have been added, however the core of the x86 instruction set was retained. And quite a lot of effort was spent making the identical directions sooner and sooner. This has change into so excessive that, though the 8086 and trendy Xeon processors can each run a standard subset of code, the 2 CPUs architecturally look about as far aside as they presumably might.

So right here we’re in the present day, with even the highest-end x86 CPUs nonetheless supporting the archaic 8086 actual mode, the place the CPU can handle reminiscence instantly, with none redirection. Having this degree of backwards compatibility could cause issues, particularly with respect to multitasking and reminiscence safety, however it was a function of earlier chips, so it’s a function of present x86 designs. And there’s extra!

I feel it’s time to place quite a lot of the legacy of the 8086 to relaxation, and let the trendy processors run free.

Some Key Phrases

To know my subsequent arguments, you might want to perceive the very fundamentals of some ideas. Trendy x86 is, to make use of the right terminology, a CISC, superscalar, out-of-order Von Neumann structure with speculative execution. What does that every one imply?

Von Neumann architectures are CPUs the place each program and information exist in the identical handle area. That is the fundamental capability to run applications from the identical reminiscence through which common information is saved; there isn’t any logical distinction between program and information reminiscence.

Superscalar CPU cores are able to working a couple of instruction per clock cycle. Which means that an x86 CPU working at 3 GHz is definitely working greater than 3 billion directions per second on common. This goes hand-in-hand with the out-of-order nature of recent x86; the CPU can merely run directions in a distinct order than they’re offered if doing so can be sooner.

Lastly, there’s the speculative key phrase inflicting all this hassle. Speculative execution is to run directions in a branching path, regardless of it not being clear whether or not mentioned directions needs to be run within the first place. Consider it as working the code in an if assertion earlier than figuring out whether or not the situation for mentioned if assertion is true and reverting the state of the world if the situation seems to be false. That is inherently dangerous territory due to side-channel assaults.

However What’s x86 Actually?

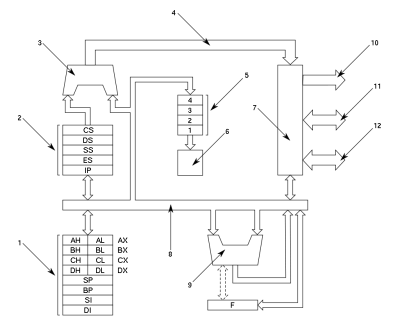

8086 block diagram by Harkonnen2

8086 block diagram by Harkonnen2

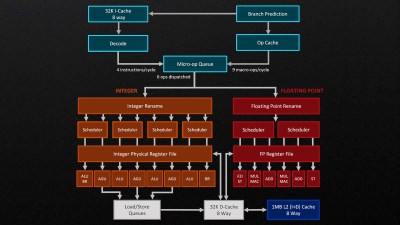

AMD’s Zen 4 structure block diagram

AMD’s Zen 4 structure block diagram

Right here, you possibly can see block diagrams of the microarchitectures of two seemingly fully unrelated CPUs. Don’t let the seems deceive you; the Zen 4 CPU nonetheless helps “actual mode”; it may possibly nonetheless run 8086 applications.

The 8086 is a a lot easier CPU. It takes a number of clock cycles to run instructionsa: anyplace from 2 to over 80. One cycle is required per byte of instruction and a number of cycles for the calculations. There may be additionally no idea of superscalar or out-of-order right here; every little thing takes a predertermined period of time and occurs strictly in-order.

In contrast, Zen 4 is a monster: Not solely does it have 4 ALUs, it has three AGUs as nicely. A few of you might have heard of the Arithmetic and Logic Unit earlier than, however Deal with Technology Unit is much less well-known. All of which means that Zen 4 can, underneath good situations, carry out 4 ALU operations and three load/retailer operations per clock cycle. This makes Zen 4 an element of two to 10 sooner than the 8086 on the identical clock velocity. For those who think about clock velocity too, it turns into nearer to roughly 5 to seven orders of magnitude. Regardless of that, the Zen 4 CPUs nonetheless helps the unique 8086 directions.

The place the Downside Lies

The 8086 instruction set will not be the one instruction set that trendy x86 helps. There are dozens of instruction units from the well-known floating-point, SSE, AVX and different vector extensions to the obscure PAE (for 32-bit x86 to have wider addresses) and vGIF (for interrupts in virtualization). Based on [Stefan Heule], there could also be as many as 3600 directions. That’s greater than twenty instances as many directions as RISC-V has, even in case you depend all the commonest RISC-V extensions.

These directions come at a value. Take, for instance one among x86’s oddball directions: mpsadbw. This instruction is six to seven bytes lengthy and compares how totally different a four-byte sequence is in a number of positions of an eleven-byte sequence. Doing so takes at the very least 19 additions however the CPU runs it in simply two clock cycles. The primary drawback is the size. The mix of the six-to-seven byte instruction size and no alignment necessities makes fetching the directions much more costly to do. This instruction additionally is available in a variant that accesses reminiscence, which complicates decoding of the instruction. Lastly, this instruction continues to be supported by trendy CPUs, regardless of how uncommon it’s to see it getting used. All that makes use of up invaluable area in cutting-edge x86 CPUs.

In RISC architectures like MIPS, ARM, or RISC-V, the implementation of directions is all {hardware}; there are devoted logic gates for working sure directions. The 8086 additionally began this fashion, which might be an costly joke if that was nonetheless the case. That’s the place microcode is available in. You see, trendy x86 CPUs aren’t what they appear; they’re truly RISC CPUs posing as CISC CPUs, implementing the x86 directions by translating them utilizing a mixture of {hardware} and microcode. This does give x86 the power to replace its microcode, however solely to alter the best way present directions work, which has mitigated issues like Spectre and Meltdown.

Happily, It Can Get Worse

Let’s get again to these pesky key phrases: speculative and out-of-order. Trendy x86 runs directions out-of-order to, for instance, do some math whereas ready for a reminiscence entry. Let’s assume for a second that’s all there may be to it. When confronted with a divide that makes use of the worth of rax adopted by a multiply that overwrites rax, the multiply should logically be run after the divide, though the results of the multiply doesn’t rely on that of the divide. That’s the place register renaming is available in. With register renaming, each can run concurrently as a result of the rax that the divide sees is a distinct bodily register than the rax that the multiply writes to.

This acceleration leaves us with two issues: figuring out which directions rely on which others, and scheduling them optimally to run the code as quick as doable. These issues rely on the actual directions being run and their resolution logic will get extra sophisticated the extra directions exist. The x86 instruction encoding format is so advanced a whole wiki web page is required to function a TL;DR. In the meantime, RISC-V wants solely two tables (1) (2) to explain the encoding of all commonplace directions. Evidently, this places x86 at an obstacle by way of decoding logic complexity.

Change is Coming

Over time, different instruction units like ARM have been consuming at x86’s market share. ARM is totally dominant in smartphones and single-board computer systems, it’s rising within the server market, and it has even change into the first CPU structure in Apple’s gadgets since 2020. RISC-V can also be progressively getting extra widespread, changing into essentially the most broadly adopted royalty-free instruction set so far. RISC-V is presently largely utilized in microcontrollers however is slowly rising in direction of higher-power platforms like single-board computer systems and even desktop computer systems. RISC-V, being as free as it’s, can also be changing into the structure of alternative for in the present day’s pc science lessons, and it will solely make it extra widespread over time. Why? Due to its simplicity.

Conclusion

The x86 structure has been round for a very long time: a 46-year very long time. On this time, it’s grown from the easy days of early microprocessors to the extremely advanced monolith of computing we have now in the present day.

This evolution has taken it’s toll, although, by limiting one of many largest CPU platforms to the roots of a comparatively historical instruction set, which doesn’t even profit from small code measurement prefer it did 46 years in the past. The complexities of superscalar, speculative, and out-of-order execution are heavy burdens on an instruction set that’s already very advanced by definition and the RISC-shaped grim reapers named ARM and RISC-V are slowly catching up.

Don’t get me fallacious: I don’t hate x86 and I’m not saying it has to die in the present day. However one factor is evident: The times of x86 are numbered.

[ad_2]

Supply hyperlink